В качестве центрального узла могут быть применены различные микропроцессоры и микроконтроллеры, например, микропроцессоры I8086, PIC - контроллеры, семейство MCS - 51. В случае использования микропроцессора потребуется подключение большого числа БИС обрамления. Поэтому рациональнее применить микроконтроллер, имеющий интеграцию всех необходимых для работы центрального микропроцессора узлов в одном кристалле.

В данном устройстве в качестве управляющего органа будет использована однокристальная микроЭВМ 80С552 фирмы Philips®. Этот кристалл содержит ядро и систему известного микроконтроллера 8051 фирмы INTEL®, но значительно превосходит его набором встроенных аппаратных средств и гибкостью их применения. Из аппаратных средств можно отметить наличие встроенных аналого-цифрового преобразователя (АЦП) и аналогового коммутатора. Следует также отметить, что данный микроконтроллер требует наличие внешнего ПЗУ. Кристалл 80C552 имеет следующие возможности:

. систему команд и архитектуру 8051. При использовании внешнего быстродействующего ПЗУ позволяет применять кварцы до 30 МГц. Нижний порог частоты возбуждения 1,2 МГц;

. внутреннее ОЗУ - 256 байт, не считая управляющих SFR регистров;

. адресует по шине до 64 кбайт внешнего ПЗУ и столько же дополнительной внешней памяти данных;

. два 16 битных таймера Т0 и Т1 стандартной архитектуры от 8051;

. дополнительный (плюс к двум стандартным) 16 - битный таймер Т2, сопряженный с 4 встроенными схемами чтения на «лету» и с 3 регистрами сравнения «на лету». Узел защелкивания позволяет аппаратно измерять интервалы на 4 диаграммах дискретных сигналов одновременно. Узел сравнения позволяет аппаратно генерировать одновременно до 8 диаграмм дискретных сигналов;

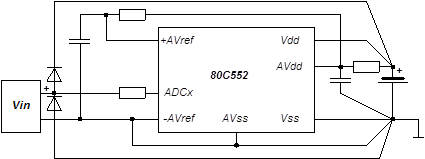

. 10-битный АЦП с 8-ми канальным мультиплексором и схемой выборки-хранения при входе. Время преобразования 37,5 мкс при частоте кварца 16 Мгц. Опорное напряжение задается внешним источником. Аналоговые схемы имеют изолированные от цифровых цепей входы питания плюс Avdd и аналоговый общий Avss. Это позволяет значительно уменьшить шумы. Общий Avss должен подсоединяться внешними цепями к цифровому общему Vss в оптимальной для конкретной схеме точке (уменьшение импульсных шумов из-за бросков тока). Положительное питание Avdd не должно превышать уровень питания цифровых цепей кристалла более чем на 0,7 В. Его следует фильтровать от импульсных помех. На рис. 3.1.1 приведена схема подключения некоторого источника сигнала Vin к одному из 8-ми входов аналогового мультиплексора ADCx.

микроконтроллер память программа стабилизатор

Рисунок 3.1.1. Схема питания встроенного АЦП

Здесь реализована простая RC-фильтрация питания аналоговых цепей кристалла и опорных напряжений. Предусмотрена защита с помощью диодов входа 80С552 от электрического пробоя при случайном выбросе напряжения на входе Vin. Наилучший динамический диапазон АЦП дают значения опорных напряжений дают значения опорных напряжений равные + AVref = AVdd и - AVref = AVss. При этом опорные напряжения не должны выходить за указанные пределы более чем на 0,2 В.

. два независимых 8 - битовых ШИМ генератора с программно регулируемым периодом следования (могут использоваться как выходы ЦАП);

. пять стандартных портов ввода-вывода. Из них два использованы как микропроцессорная шина, а остальные имеют альтернативные функции;

. сторожевой таймер T3.

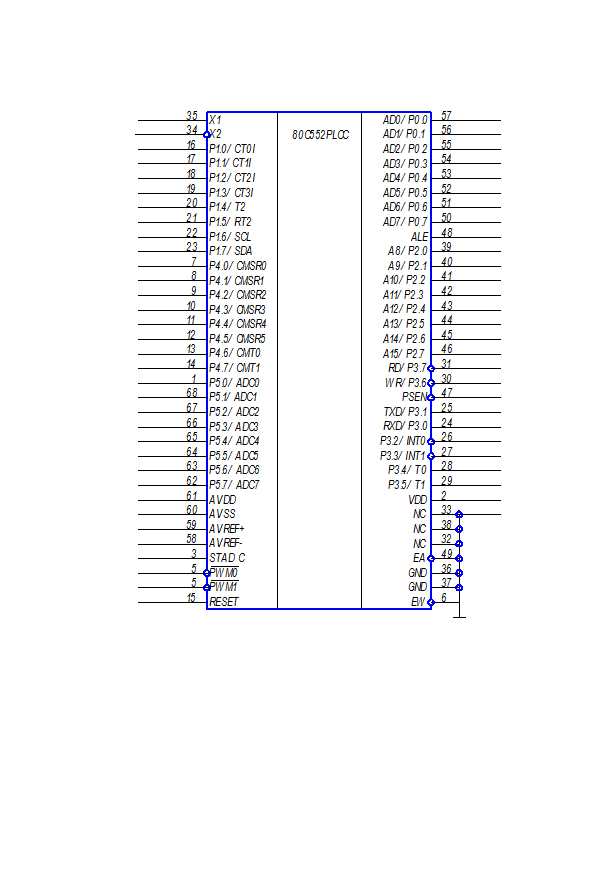

Условное обозначение 80С552 показано на рисунке 3.1.2.

Рисунок 3.1.2 Условное обозначение 80С552

В таблице 3.1. приведены обозначения и назначение выводов кристалла 80С552.

Таблица 3.1. Назначение и номера выводов 80С552

| Обозначение | Ножка | Назначение выводов и альтернативные функции |

| VDD | 2 | Питание +5 В цифровых схем кристалла |

| STADC | 3 | Внешний пуск АЦП. Пуск может быть и по программе. Не оставлять этот вывод висящим в воздухе. |

| /PWM0 | 4 | Инверсный Выход ШИМ генератора 0 |

| /PWM1 | 5 | Инверсный Выход ШИМ генератора 1 |

| /EW | 6 | Инверсный Вход разрешения встроенному сторожевому таймеру Т3. Не оставлять этот вывод висящим в воздухе. |

| P0.0 - P0.7 | 57…50 | Порт0. Двунаправленная мультиплексированная шина данных и младших адресов А0 - А7. |

| Р1.0 - Р1.7 | 16…23 | Порт1. Двунаправленный порт. Имеет следующие альтернативные функции: |

| CT0I - CT3I | 16…19 | Входы для четырех схем захвата таймера Т2. |

| T2 | 20 | Вход внешних импульсов для таймера Т2 (могут быть внутренние) |

| RT2 | 21 | Вход внешнего сброса для таймера Т2 |

| SCL | 22 | Линия синхронизации последовательной шины I2C SCL |

| SDA | 23 | Линия данных последовательной шины I2C SDA |

| Р2.0 - Р2.7 | 39…46 | Порт2. Выход старшей половины адреса А8 - А15 |

| Р3.0 - Р3.7 | 24…31 | Порт3. Двунаправленный порт. Имеет следующие альтернативные функции: |

| RxD | 24 | Вход UART |

| TxD | 25 | Выход UART |

| /INT0 | 26 | Инверсный вход внешнего сигнала прерывания 0 |

| /INT1 | 27 | Инверсный вход внешнего сигнала прерывания 1 |

| T0 | 28 | Вход внешних импульсов для таймера_0 (могут быть внутренние) |

| T1 | 29 | Вход внешних импульсов для таймера_1 (могут быть внутренние) |

| /WR | 30 | Инверсный Выход строба записи во внешнюю память данных |

| /RD | 31 | Инверсный Выход строба чтения из внешней памяти данных |

| Р4.0 - Р4.7 | 7…14 | Порт4. Двунаправленный порт. Имеет следующие альтернативные функции: |

| CMRS0 - CMRS5 | 7…12 | Выходы с установкой или сбросом при достижении таймером Т2 заданного значения |

| CMТ0 - CMТ5 | 13, 14 | Выходы с изменением на противоположный логического уровня при достижении таймером Т2 заданного значения |

| Р5.0 - Р5.7 | 68… 62, 1 | Порт5. Двунаправленный порт. Имеет альтернативные функции в виде аналоговых каналов мультиплексора ADC0 - ADC7 АЦП |

| RST | 15 | Вход для сигнала сброса процессора. Когда срабатывает сторожевой таймер Т3, то RST генерится на этой ножке изнутри |

| XTAL1 | 35 | Подключение кварца. Также вход от внешнего источника возбуждения кристалла |

| XTAL2 | 34 | Подключение кварца. Когда используется внешнее возбуждение через ввод XTAL1, оставить этот вывод висящим в воздухе. |

| VSS | 36,37 | Две ножки общего вывода. Использовать обе. |

| /PSEN | 47 | Инверсный выход строба чтения из внешней памяти программ |

| ALE | 48 | Выход строба для защелкивания младшей половины адреса |

| /EA | 49 | Инверсный Вход для указания, что процессор должен использовать внешнюю память программ. Не оставлять висящим в воздухе. |

| -AVref | 58 | Подвод нижнего уровня опорного напряжения, но не ниже АVSS. Соответствует результату АЦП = 0. |

| +Avref | 59 | Подвод верхнего уровня опорного напряжения. но не выше АVDD. Соответствует результату АЦП = 3FFН |

| AVSS | 60 | Общий вывод аналоговых цепей кристалла |

| AVDD | 61 | Плюс питания аналоговых цепей кристалла |

Разработка датчика сетки частот генератора сигналов низкой частоты Измерением называется физический опыт, в результате которого находят численное значение измеряемой физической величины. Измерения являются важнейшим этапом деятельности работников всех ...

Определение безотказности РЭУ при наличии резервирования замещением (резерв ненагруженный) Целью данного курсового проектирования является получение (расчетным способом и моделированием отказов на ЭВМ) и сравнение показателей безотказности РЭУ при наличии резервирования замещение ...

Разработка печатного узла Современные электронные средства проектируются с использованием интегральных схем высокой степени интеграции и элементной базы, монтируемой на поверхность. Это позволяет существенно расширит ...