READY – это выходной сигнал готовности, который разрешает завершение текущего цикла шины;

RES – это входной сигнал ‘входной сброс’, который разрешает выходной сигнал RESET синхрогенератора; RESET

– это выходной сигнал, который появляется при подаче сигнала разрешения на вход RES (используется для перевода всей системы в начальное состояние);

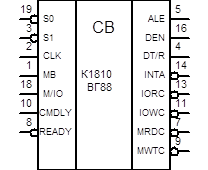

Описание шинного контроллера К1810ВГ88.

|

Конструктивно контроллер выполнен в корпусе с 20 выводами с двухрядным их расположением.

Описание выводов микросхемы: CLK – системная синхронизация, входной сигнал, идущий от синхрогенератора КП1810ГФ84; S0,S1,M/IO – это входные сигналы, с дешифрации которых контроллер начинает свою работу по выполнению совместно с процессором очередного цикла шины ( расшифровка различных комбинаций этих сигналов приведена при описании выводов процессора с теми же названиями);

МВ

– это входной сигнал выбора режима шины MULTIBUS;

READY

– сигнал на этом входе, указывает на окончание текущего цикла шины;

CMDLY

– этот входной сигнал позволяет задержать начало работы контроллера по выполнению очередного цикла шины; CENL

– это входной сигнал, называемый разрешением защелкивания команды (в PC/AT на этот вход должна подаваться логическая единица);

CEN/AEN

– это входной сигнал, называемый ‘разрешение команды/разрешение адреса’;

ALE – это выходной сигнал, называемый ‘разрешение защелки адреса’;

DEN

– это выходной сигнал разрешения передачи данных, определяет передачу данных со входов на выходы в шинных формирователях, подсоединенных к системной шине; DT/R – это выходной сигнал, определяющий направление передачи данных ( микросхема DD14 используется для передачи младшего байта данных, а DD13 – старшего байта данных);

MCE – это выходной сигнал разрешения каскадирования (в PC/AT не используется); INTA

– это выходной сигнал подтверждения аппаратного прерывания;

IORC – это выходной сигнал управления, сообщающий периферийному устройству, что оно должно выставит данные на шину для последующего их чтения процессором;

IOWC - это выходной сигнал управления, информирующий о протекании цикла шины записи данных в периферийный порт; MRDC

– это выходной сигнал, сообщающий о проведении цикла шины чтения данных из ОП; MWTC

– этот выходной сигнал информирует о протекании цикла шины записи данных в ОП.

Описание буферного регистра КП580ИР82.

Используется для организации запоминающих буферов, адресных защелок, портов ввода-вывода и тому подобное. Буферные регистры состоят из восьми информационных триггеров с трехстабильными выходами, общими сигналами записи информации и управления выходными схемами.

|

Назначение выводов: D7 – D0 – линии входных данных; Q7 – Q0 – линии выходных данных; C- стробирующий сигнал; CS – разрешение выдачи данных. Регистр принимает и отображает информацию синхронно с положительным перепадом тактового импульса, подаваемого на вход С. Состояния регистра приведены в таблице.

|

| Входы | Выход триггера | Выходы | ||

| CS | С | Dn | Q | Q0 Q7 | |

|

| 0 | 0 | 0 | 0 | |

| 0 | 1 | 1 | 1 | ||

|

| 1 | 0 | 0 | Z | |

| 1 | 1 | 1 | Z | ||

Разработка конструкции и технологического процесса изготовления печатной платы Основной особенностью производства ЭВМ является использование большого количества стандартных и нормализованных элементов, интегральных схем, радиодеталей и др. Важным вопросом, решаемы ...

Принципы построения систем спутниковой связи Сегодня растут потребности в телекоммуникациях. Наземные радиорелейные линии не могут в полной мере удовлетворить обмен радиовещательных и телевизионных программ, особенно если они ...

Моделирование голограммы, получаемой с помощью подповерхностного сканирующего радиолокатора Современные радиолокаторы можно условно разделить условно на два класса: радиолокаторы в которых используются видеоимпульсные сигналы и радиолокаторы с использованием гармонических модулиро ...