Анализ принципиальной электрической схемы проводим на ПК с помощью системы проектирования электронных устройств OrCAD 9.2.

Первоначально проведем анализ блоков схемы для проверки функционирования каждого из них.

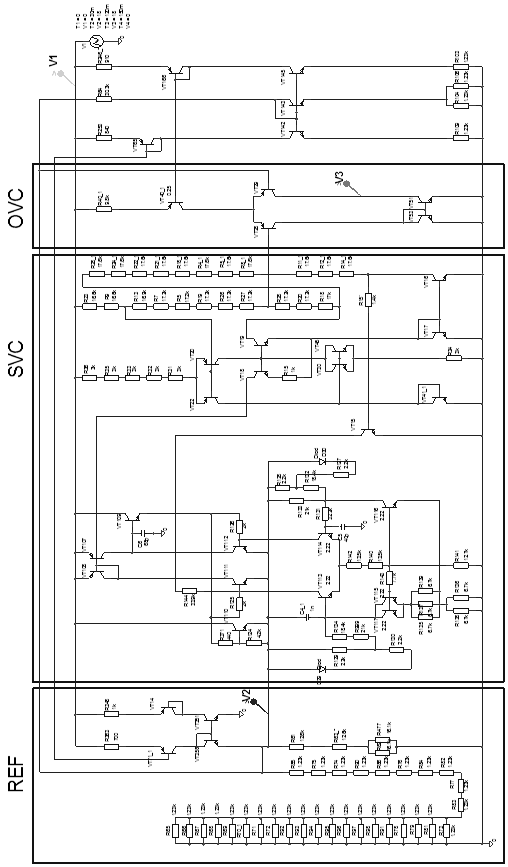

Проанализируем сначала цепи питания ИМС. Как видно из структурной схемы (приложение А) Основными блоками цепи питания являются: источник опорного напряжения - REF, компаратор напряжения питания – SVC и компаратор перенапряжения - OVC. На рисунке 3.1 приведена электрическая принципиальная схема трех этих каскадов.

Источник опорного напряжения (REF) должен вырабатывать напряжение 5±0.15В (см таблицу 3.11), независимо от напряжения питания микросхемы.

Компаратор напряжения питания – компаратор с гистерезисом. Согласно таблицы 3.1, верхний порог переключения этого компаратора составляет 15±0.5В, Нижний порог переключения 8±0,5В. Компаратор включен таким образом, что управляет опорным напряжением. При срабатывании компаратора, он разрешает либо блокирует подачу опорного напряжения на всю схему, таким образом он включает или выключает ИМС.

Компаратор перенапряжения – защита от перенапряжения по цепи питания, порог срабатывания которого согласно 16,5±0.5В (таблица 3.9).

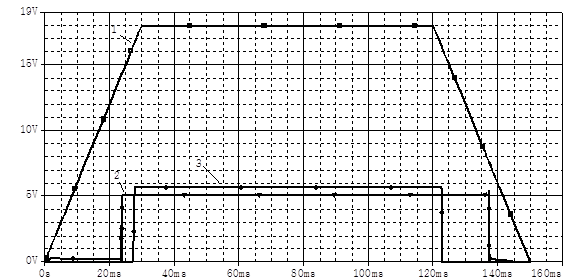

Результаты компьютерного моделирования описанных блоков приведены на рисунке 3.2. Как видно из диаграмм все блоки выполняют свои функции, причем значения потенциалов полученные при моделирования совпадают с указанными в технической документации на ИМС TDA16846.

Рис.3.2

Рисунок 3.2 – Диаграммы работы блоков ИМС по цепи питания.

1 – Напряжение источника питания;

2 – Напряжение стабилизатора;

3 – Диаграмма срабатывания компаратора защиты от превышения напряжения питания

Промоделируем работу выходного каскада ИМС совместно с логическим элементом G3 на его входе. Сигналы управления будем подавать на входы логического элемента. Логический элемент представляет из себя 3-х входовой элемент “И”- G3 (Приложение А). Как видно из структурной схемы, на верхний и нижний входы элемента подаются сигналы защиты, то есть в отсутствии “аварийных ситуаций” на этих входах присутствуют уровни напряжения соответствующие логической единице. На средний же вход подается управляющие импульсы прямоугольной формы с частотой порядка 20-100 кГц.

Согласно таблицы 3.14 верхний уровень выходных импульсов должен составлять 10±0.5 В, нижний уровень 1,5 – 2,4 В

Для моделирования на два входа G3 подаем постоянные потенциалы 1 В посредством источников V2, V3. На оставшийся вход подаем импульсное напряжение посредством источника V4. Уровни импульсов нижнего и верхнего примем 0 и 1В соответственно, а частоту 20кГц.

В качестве нагрузки вместо МОП-транзистора включаем эквивалентную нагрузку – резистор RH1.

Схема электрическая принципиальная выходного каскада (Output Driver) и логического элемента G3 приведена на рисунке 3.3.

Диаграмма работы данных блоков приведена на рисунке 3.4.

Как видно из диаграмм полученные результаты удовлетворяют необходимым в соответствии с техническим описанием на ИМС TDA16846.

| Рисунок 3.3 - Схема электрическая принципиальная выходного каскада с логическим элементом на входе. |

Разработка технологического процесса сборки измерителя H21э транзисторов При современном конструировании радиоэлектронных аппаратов необходимо в первую очередь учитывать конструктивно-технологические особенности РЭА, включают функционально-узловой принцип ко ...

Прием и выплата электронных переводов В октябре 2007г. ФГУП "Почта работы" начала реализацию проекта по Модернизаций системы электронных переводов. Основная цель проекта-Повысить доступность и качество оказываемых ...

Домашние и офисные сети Home Lan - стандарты и оборудование (Home lan и интеллектуальный дом) Система "Умный дом": Нужна для облегчения управления домашним хозяйством, а также для расширения его возможностей. Предлагаемая система является самой передовой технологией ...