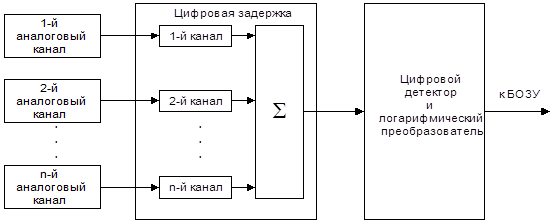

Рисунок 5. Аналоговый тракт современного УЗ сканера

|

Рисунок 6. Цифровое преобразование параметров эхо-сигнала

Выходные сигналы аналоговых трактов апертуры уже в цифровой форме направляются в свои каналы цифровой задержки и затем суммируются цифровым сумматором. Результирующий цифровой эхо-сигнал подвергается цифровому детектированию, а затем – логарифмированию. Отметим, что в полностью аналоговых трактах эти процедуры протекали в другой последовательности.

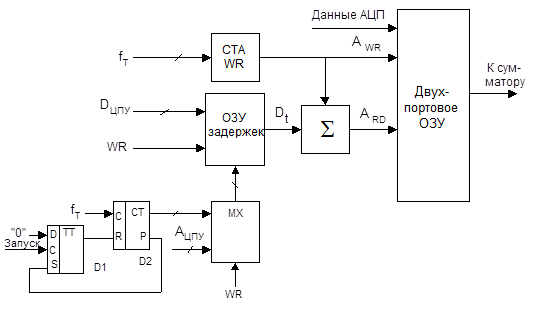

Цифровая задержка эхо-сигналов основана на сдвиге во времени результатов АЦ-преобразования каждого канала по отношению к моменту окончания преобразования. Структурная схема одного канала цифровой задержки показана на рис. 7.

|

Поступающие с АЦП данные записываются в двухпортовое ОЗУ по адресам AWR, выставляемым счетчиком СТА, а считываются эти данные по адресам ARD. Они представляют собой сумму адреса AWR и данных, которые устанавливаются в ОЗУ задержек. Сразу после записи данных АЦП происходит переключение в режим чтения, и данные из ОЗУ задержек начинают суммироваться с адресом AWR. Через некоторое число тактов fT наступает равенство ARD и AWR, по которому была произведена запись данных АЦП. Это число тактов и величина fT и определяют время задержки. В этом же канале производят апподизацию – умножение выходного сигнала на некоторый коэффициент, который записывается в то же ОЗУ, что и задержки. Апподизация предназначена для формирования желаемой характеристики направленности антенной решетки при приеме (например, для исключения боковых лепестков).

Раньше было показано, что различие в задержках соседних каналов апертуры составляет десятки нс. Поэтому для точной установки задержек тактовая частота должна быть очень высокой – 50 – 100 МГц. Очевидно, что такой же должна быть и частота преобразования АЦП. Она намного выше той, которая была рассчитана в начале раздела 2.6. Конечно, в проектировании таких АЦП возникают определенные сложности (экранирование блока и др.). Однако при такой высокой скорости преобразования появляется возможность формировать точку фокуса на каждом дискретном отсчете вдоль луча, т.е. получается фокус, следящий за движением фронта отраженного сигнала. Естественно, это дает повышение четкости изображения.

На рис.8 приведена структурная схема блока цифрового детектора и логарифмического преобразователя. Здесь завершается подготовка сигналов перед их записью в буферное ОЗУ. Еще раз подчеркнем, что все в этом блоке – цифровое! Перейти на страницу: 1 2 3 4 5

Советуем почитать:

Многопроцессорный вычислительный комплекс Вычислительная техника в своем развитии по пути повышения быстродействия ЭВМ приблизилась к физическим пределам, которые обусловлены ограниченной скоростью распространения сигналов в лин ...

Проектирование узла цифрового комбинационного устройства Цель работы - проектирование узла цифрового комбинационного устройства. Составление модели проектируемого устройства с помощью программы Electronics Workbench. Научная новизна отсу ...

Определение надежности устройства РЭА Полупроводниковая электроника – прогрессирующая область науки и техники. Уже в первом десятилетии с момента изобретение транзисторов полупроводниковые приборы нашли широкое применение в ...